Original Research Paper

# Design and Development of Multilevel Inverter for Convert Direct Current to Alternating Current Using MATLAB Simulation

Afnan Rusyaidi Abu Bakar<sup>1, 2</sup>, Nashiren Farzilah Mailah<sup>1</sup>, Abu Bakar Ibrahim<sup>2</sup>

<sup>1</sup> Faculty in Engineering, Universiti Putra Malaysia. Sedang Selangor, Malaysia.

Article history 15.02.2022

**Revised:** 14.03.2022

**Accepted:** 19.03.2022

\*Corresponding Author:

Abu Bakar Ibrahim

Email:

abubakar.ibrahim@fskik.upsi.edu.my

This is an open access article, licensed under: CC-BY-SA

Abstract: This paper presented the design and development of a multilevel inverter (MLI). The demand for better electronic devices increases rapidly. The multilevel inverter (MLI) which convert direct current (DC) to alternating current (AC) are widely used in the industry. The objective of this research is to design and simulate the 3-level and 3-level NPC MLI module using PLECS software. To develop the switching technique for each level of NPC MLI, and To analyse and validate the MLI in terms of harmonic. Although there is already an inverter in the market, the researcher still pursues to improve the efficiency, total harmonic distortion (THD), and reduce the size of the MLI. A THD can be improved using the suitable modulation technique and the size of the MLI can be reduced by designing better topologies. The modular NPC is using the three-level NPC as the main module and the number of levels can be increased by adding 2 level NPC modules to the main module. The switching technique was created to control the NPC MLI for each level.

Keywords: Multilevel Inverter, Selective Harmonic Limitation, THD.

<sup>&</sup>lt;sup>1</sup> Department of Computing, Faculty of Arts, Computing and Creative Industry. Universiti Pendidikan Sultan Idris. Tanjong Malim, Malaysia.

#### 1. Introduction

In a power system, the power electronic devices are utilized in an inverter and control of electrical power. The inverter in the power system fits both tasks by converting DC to AC and controlling the frequency of the AC which is the output. The multilevel inverter is used to produce a sinusoidal voltage waveform from several levels of DC voltage. However, a two-level voltage source converter incapable to get good system performance and efficiencies such as optimum filter size, THD and losses. The improved performance and efficiency of a high voltage system can be achieved by the use of a multilevel inverter [1]. As the level of inverter increases, the stress on each device can be reduced proportionally, which leads to increased voltage handling capacity of inverter and avoids a bulky & expensive step-up transformer from the application [2]. In this research, we try to achieve the goal to reduce stress on each device by adding a module to increase the number of levels for NPC MLI. To achieve the desired output AC voltage the semiconductor devices in the inverter must be controlled using a way that can minimize the harmonic. The commonly available switching technique is the selective harmonic elimination (SHE) method at the fundamental frequency, for which transcendental equations characterizing harmonics are solved to compute switching angles [3] [4].

#### 2. Literature Review

An inverter is an essential part of any renewable energy power conversion for converting the power from DC to AC. The inverter output can be classified into two types such as square wave (two-level) and quasi square wave (three-level or modified square wave) [5]. Although the square wave and quasi-square wave inverters can be adequate for some viable applications which are still accessible in the market they are not prescribed to new plans because of their exceptionally low-quality waveform [5] [6]. To overcome this drawback, a multi-stepped waveform was introduced by the multilevel inverter (MLI) concept. MLI waveform can be divided into two types such as low-frequency multistepped waveform and high-frequency multi-stepped waveform using pulse width modulation (PWM). Passive filters are essential to obtain a sinusoidal output voltage waveform. High-frequency multistep waveform requires fewer passive filters when compared to other waveforms [6]. MLI comprises an array of the power semiconductor devices and DC/capacitor voltages which generates output voltage levels with stepped waveform [7]. The aim of MLI is to generate a near sinusoidal voltage waveform with several steps by utilizing the proper switching signal of the semiconductor devices and isolated or non-isolated DC voltage sources [8]. Increasing the number of levels in the output waveform leads to attaining pure sinusoidal voltage without expensive passive filters and bulky transformers [8] [9]. In low voltage applications, the two-level inverter can be used but MLI can achieve more in terms of voltage THD and losses. Because when the level of MLI increases then the near-perfect sinusoidal voltage is achieved thus resulting in the better voltage THD and less harmonic.

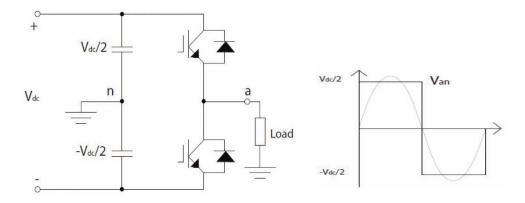

Figure 1 shows one phase limb of a two-level inverter and two-level waveform without PWM [10].

Figure 1. One phase Limb of a Two-Level Inverter and a Two-Level Waveform without PWM

In paper Koshti & Rao [11] the author discusses about the MLI topologies and the control strategies. The input voltage can be obtained from dc battery, energy storage capacitors or any kind of renewable energy sources.

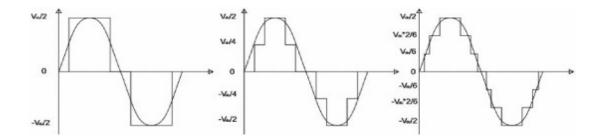

Figure 2. Level Waveform, 5-Level Waveform and a 7-Level Multilevel Waveform [11].

In Figure 2 the different of each level of inverter make the difference in sinusoidal wave. Based on Figure 2, the waveform become more sinusoidal as the level increase.

## 2.1. Neutral Point Clamped

The neutral point clamped (NPC) three-level inverter was first introduced by A. Nabae, I. Takahashi and H. Akagi in 1980 and published in 1981 [3]. With this circuit configuration, the voltage stress on its power switching devices is half that for the conventional two-level inverter. Because of this nature, it was applied to medium and high voltage drives [10]. The NPC inverter has lower line-to-line and common-mode voltage steps, more frequent voltage steps in one carrier cycle, and a lower ripple component in the output current for the same carrier frequency [10]. These are significant merits for motor drives over the conventional two-level inverters in the form of lower stress to the motor windings and bearings.

Figure 3 shows the circuit diagram of the NPC three-level inverter. This is also a three-phase inverter.

Figure 3. The neutral Point Clamped Three-Level Inverter Circuit Topology [10]

In Figure 3, when IGBTs QU1 and QU2 are turned on, output U is connected to the positive rail (P) of the dc bus. When QU2 and QU3 are on, it is connected to the mid-point (0) of the dc bus, and when QU3 and QU4 are on, it is connected to the negative rail (N) [10].

Table 1 shows the relation between the Switching States and Output Voltage [10].

|                    | Qui | Q <sub>u2</sub> | Qu3 | Q <sub>u4</sub> | $V_{u}$ |

|--------------------|-----|-----------------|-----|-----------------|---------|

| Switching<br>State | ON  | ON              | OFF | OFF             | +E/2    |

|                    | OFF | OFF             | ON  | ON              | -E/2    |

|                    | OFF | ON              | ON  | OFF             | 0       |

Table 1. Relation between Switching States and Output Voltage

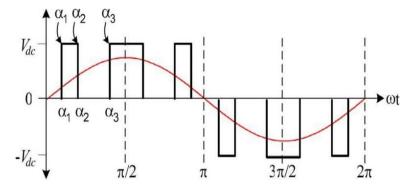

#### 2.2. Selective Harmonic Elimination

Selective Harmonic Elimination (SHE) is a fairly good technique for controlling the three-level inverter. This is because the equipment needs to operate at very low frequency to reduce the semiconductor losses. Figure 2.2 shows the load voltage generated by a three-level NPC inverter. Using three switching angles  $\alpha 1$ ,  $\alpha 2$ , and  $\alpha 3$  and  $90^{\circ}$  symmetry, three harmonics can be controlled [12]. SHE-PWM is based on the Fourier series decomposition of the periodic PWM voltage waveform generated by the power electronics converter [13].

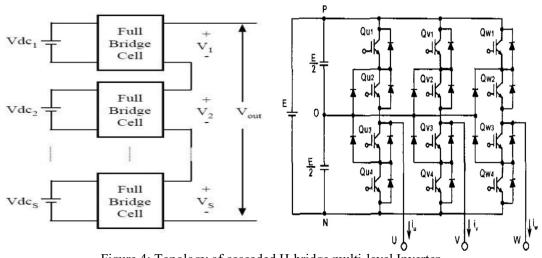

SHE technique is used to optimize switching angles of a cascaded multilevel inverter so as to produce required fundamental voltage along with improved staircase waveform in terms of total harmonic distortion (THD). Number of nonlinear transcendental equation will be s and number of harmonics to be eliminated becomes (s-1) in SHE formulation if the number of cells used in cascade multilevel inverter is s per phase. The most important part of the UPS is the inverter. Usually designed using Cascaded H-bridge MLI technology. Cascaded H-bridge multilevel technology is more appropriate for this particular application as the input is in the form of four separate batteries, which are used to achieve a stepped AC voltage waveform at the output [14].

Figure 4 shows topology of cascaded H-bridge multi-level Inverter [14].

Figure 4: Topology of cascaded H-bridge multi-level Inverter

The voltages of each of the four batteries are approximately equal and thus equal step size is

assumed, reducing the complexity of the controller. Therefore, this can be identified as a symmetrical source inverter. Furthermore, the use of equal size batteries gives the advantage of easy replacement as well [14]. The relationship between the number of DC sources and the output levels are given by the following equation [15].

#### 3. Methodology

The progress for the research completion will be discussed in this chapter. Besides of the literature review, the methodology involves designing, simulation, hardware development and experimental work. This method is used to make sure the progress of the research will be more systematic. This research which is "Design and Development of Multilevel Inverter" requires the designing and development process. The designing process require several approaches same with the development process. Before the development process, there are simulation process which is very important in this research. Figure 5 shows the flowchart of the research.

Figure 5. Flowchart of the Research

In this research the PLECS software will be used. This software is similar to the MATLAB Simulink but PLECS is simpler. Besides this software require a less storage than MATLAB Simulink which has bigger files. PLECS also provided better parameter option for each component in simulation thus make the designing and simulation process easier. In this research the 3-level MLI were used. This 3-level MLI will be the main circuit for MLI module. Another reason why 3-level MLI were chosen instead of 2-level MLI was the waveform of 3-level MLI were more sinusoidal than

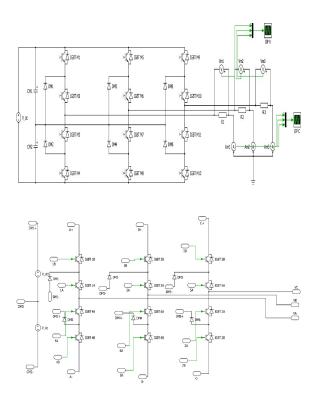

2-level MLI waveform. Figure 6 shown the research designs the MLI circuit for 3 phase application. For these 3 phases the number of IGBT become 12 in the circuit.

Figure 6. MLI circuit for 3 Phase Application

### 4. Results

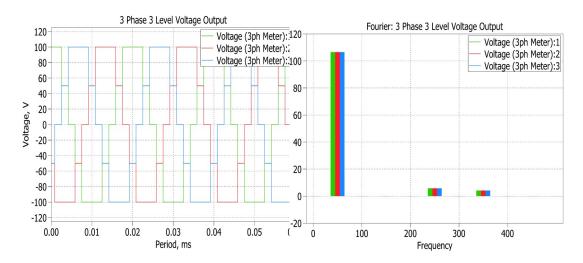

The circuit consist of 12 switches with 12 switching signals. By using pulse generator, the switching signal with different duty cycle and phase delay is entered. The voltage source is 100V and the capacitor is replaced by 25V voltage source to simulate the voltage levels by capacitor. As shown in Figure 7 the voltage output for 3 level is recorded. They are flowing smoothly and didn't show any break.

Figure 7. The Fourier Spectrum for 3 Level NPC MLI

#### 5. Conclusion

The Neutral Point Clamped Multilevel Inverter module shows that as the inverter level increases, the THD also decreases accordingly. The 3th harmonics found in the system can be reduced by using filters. Levels can be raised further over 11 levels to get a lower THD by using the MLI NPC module. Although THD is still high compared to other switching techniques this technique will be able to compensate by using a high level of MLI NPC. But using high-level MLI NPCs will increase the cost of the system. The switching for this circuit can be further enhanced to reduce THD even at lower levels.

#### References

- [1] A. M. Y. M. Ghias, J. Pou, M. Ciobotaru, V. G. Agelidis, "Voltage balancing strategy for a five-level flying capacitor converter using phase disposition PWM with sawtooth shaped carriers," in *IECON 2012 38th Annual Conference on IEEE Industrial Electronics Society*, pp.5013-5019, 2012.

- [2] S. K. Bisoyi and N. K. Agarwal, "SHE PWM technique for three phase three level voltage source inverter," 2017 IEEE International Conference on Power, Control, Signals and Instrumentation Engineering (ICPCSI), Chennai, pp. 1742-1746, 2017

- [3] A Nabae, I. Takahashi and H. Agaki, "A New Neutral-Point-Clamped PWM Inverter," *IEEE Transactions on Industry Applications*, vol. 17, no. 5, pp. 518-523, 1981.

- [4] P.M. Bhagwat and V.R. Stefanovic, "Generalized Structure of a Multilevel PWM Inverter," *IEEE Transactions on Industry Applications*, vol. 19, no. 6, pp. 1057-1069, 1983.

- [5] I. Colak, E. Kabalci and R. Bayindir, "Review of Multilevel Voltage Source Inverter Topologies and Control Schemes Energy Convers Manage," *IEEE Electronic*, vol. 52, no. 11, pp. 14-28, 2011.

- [6] J. Rodriguez, J. S. Lai, F. Z. Peng, "Multilevel Inverters: A Survey of Topologies, Controls and Applications. *IEEE Trans Electron*, vol. 49, no. 4, pp. 38-724, 2002.

- [7] M. Islam, S. Mekhilef and M. Hasan, "Single Phase Transformer-Less Inverter Topologies for Grid-Tied Photovoltaic System: A Review. Renew Sustain Energy, vol. 45, pp. 69-86, 2015.

- [8] M. P. K. K. Kowski, L. G. Franquelo, J. Rodriguez, A. Perez and J. I. Leon, "High Performance Motor Drives," *IEEE Ind Electron Mag*, vol. 5, no. 3, pp. 6-26, 2011.

- [9] S. Kour, M. Malinowski, K. Gopakumar, J. Pou, L. G. Franquelo, B. Wu, J. Rodriguez, M. A. Pérez and J. I. Leon, "Recent Advances and Industrial Applications of Multilevel Converters. *IEEE Trans Ind Electron*, vol. 57, no. 80, pp. 25-53, 2010.

- [10] H. Krug, T. Kume and M. Swamy, "Neutral-point clamped three-level general purpose inverter - features, benefits and applications," 2004 IEEE 35th Annual Power Electronics Specialists Conference (IEEE Cat. No.04CH37551), Aachen, Germany, 2004, pp. 323-328 Vol.1.

- [12] H. S. Patel and R. G. Hoft, "Generalized Techniques of Harmonic Elimination and Voltage Control in Thyristor Inverters: Part I Harmonic elimination," *IEEE Trans. Ind. Appl*, vol. 9, no. 3, pp. 310–317, 1973.

- [13] J. Rodriguez, S. Bernet, P. K. Steimer and I. E. Lizama, "A Survey on Neutral-Point-Clamped Inverters," in *IEEE Transactions on Industrial Electronics*, vol. 57, no. 7, pp. 2219-2230, July 2010

- [11] A. K. Koshti and M. N. Rao, "A brief review on multilevel inverter topologies," 2017 International Conference on Data Management, Analytics and Innovation (ICDMAI), pp. 187-19, 2017.

- [14] P. D. H. Darmawardana, T. D. Kahingala, K. M. C. G. Karunarathna, L. B. S. N. Kularatne and J. P. Karunadasa, "Nine level cascaded H Bridge Inverter for High Performing UPS Applications," 2015 Moratuwa Engineering Research Conference (MERCon), pp. 76-81, 2015.

- [15] Kamaldeep and J. Kumar, "A new 7-level asymmetrical multilevel inverter with reduced number of sources and switching components," 2016 7th India International Conference on Power Electronics (IICPE), pp. 1-5, 2016.